| 板级电路高密度、高精度组装技术(2) | |

| 2012-10-18 10:51:21 | |

| 3.2 高密度印制电路板丝网漏板的设计和制作

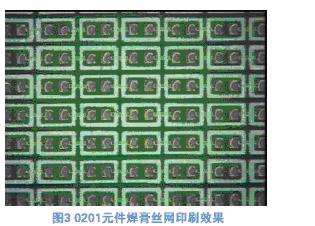

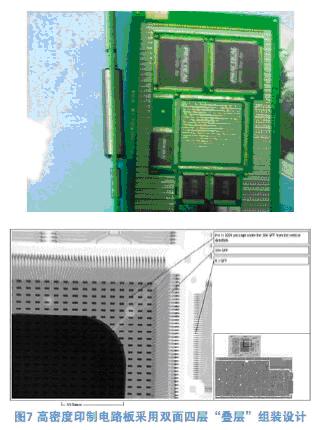

高密度印制电路板设计和制作后,课题设计研究的重点攻关内容是高密度印制电路板丝网漏板的设计和制作;高密度印制电路板采用了0201元件和引脚中心距为0.3mm的QFP,对丝网漏板的设计和制作的要求极高,传统的激光刻蚀已不能满足高密度丝网漏板的加工要求;高密度丝网漏板设计和加工是一个带全局性的关键技术。 0201元件及引脚中心距为0.3mmQFP最佳加工方法是采用电铸法制造出0.08~0.10mm丝网模板,模板均匀度为3~5um/m2。其次是采用激光+电抛光,加工出厚度为0.1mm的丝网模板。 面积比=开口面积(LxW)/孔壁的面积〔2x(L+W)xT〕>0.66。(L为开口长度) 宽厚比(Aspect Ratio)=开口的宽度(W)/模板的厚度(T)>1.5。 在完成高密度印制电路板丝网漏板设计的基础上,通过调研落实能保证含有0201元件和引脚中心距为0.3mm的QFP丝网漏板加工质量的协作单位,完成了高密度工艺样板的制作;高密度丝网模板选用激光+电抛光加工方法,丝网模板是厚度为0.1mm的不锈钢板。 3.3 高密度印制电路板组装工艺试验 根据已确定的合格的高密度印制电路板试验样板,完成高密度组装中特殊新型工艺的应用研究,进一步完善高密度设计要求、高密度组装工艺方案的可靠性,为后期型号产品的高密度组装应用的一次成功率的可能性确立坚实的基础! 针对高密度印制电路板组装技术上的难度,以《高密度印制电路板组装工艺试验方案》为技术依据,以高密度印制电路板为试验对象,制定组装工艺试验实施方案;关键工艺的实现以国内先进组装技术、设备为依托进行高密度印制电路板组装工艺试验为第一方案,以手动或半自动SMT组装生产线的工艺装备、技术资源为依托进行高密度印制电路板组装工艺试验为备份方案;通过试验初步了解和掌握高密度印制电路板在具有国际先进技术水平的全自动SMT生产线的组装工艺技术。 1)组装工艺流程 ·试验分析 在完成组装试验前的技术准备工作条件下,具体试验过程中0201及引脚中心距0.3mmQFP的组装焊接都不构成试验的关键技术;高密度印制电路板组装试验的关键技术是能否把双面四层元器件,即A、B两面的0201元件及304脚QFP器件分别能一次焊好;如能一次焊好,这是最理想的。第一块工艺样板板A面焊接后用X光检测,如发现0201元件及304脚QFP器件不能同时焊好,采用特殊SMT工艺流程。 2)关键组装工艺技术 (1)温度阶梯焊工艺 由于PCB板A、B两面贴装高密度芯片(QFP、uBGA、CSP、TSOP、SOT、PQFP),然后在其四周贴装0402片式电阻、电容;并在PCB板A、B两面的304脚PQFP下面均贴装了0201片式电阻、电容。则在焊接工艺中拟采取温度阶梯焊工艺。即对PCB的A面元器件应用无铅焊料,而对PCB的B面元器件应用Sn/Pb焊料;对PQFP采用低温焊料。 (2)焊膏丝印工艺技术

由于PCB的A、B两面的304脚QFP的下面均贴装了805个0201元件,304脚QFP与0201元件之间的距离只不到0.1mm,除了必须严格控制丝网模板的厚度、均匀度外,还必须严格控制刮刀速度、刮刀压力和离板速度,保证焊膏的均匀度。 3)高密度印制电路板组装工艺试验步骤 (1)焊膏印刷试验: 用1块高密度印制电路板进行丝网模板与印制板的对位、焊膏印刷试验;调节各项印刷参数。

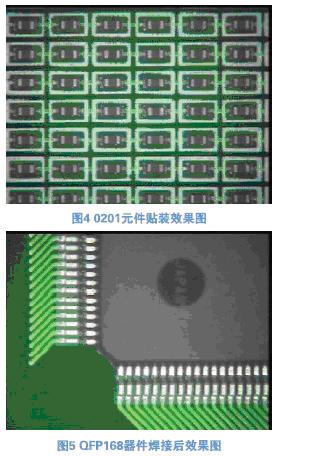

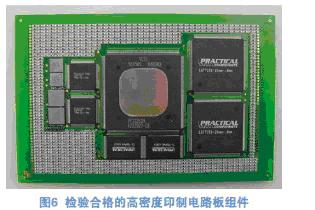

(2)组装工艺全过程试验 用1块高密度印制电路板进行从丝印、贴片、焊接的组装工艺全过程试验,调整回流焊温度曲线,重点检测双面四层0201元件及304脚QFP器件的焊接质量; (3)进行组装工艺试验,调整修改各项工艺参数; (4)高密度印制电路板组装工艺验证 4 结束语 超小型0201和0402chip及细间距QFP、CSP和uBGA的应用,使组装密度达到高密度、高精度的目的,在通讯设备及计算机中今后大量应用的是双面(或多层)PCB高密度“叠层”组装技术,可以认为,双面(或多层)PCB高密度“叠层”组装技术是一种有着广泛应用前景的电子组装技术。 目前,高密度组装的设计思维已融入型号产品PCB的系统设计中,该项成果的推广应用将使我国电子装备中电路模块的面积在原有的基础上缩小1/3,重量减轻1/3,电路模块功能进一步扩展,促进和推动我国军事电子装备的板级电路组装上水平。 除此以外,该项目工艺技术研究内容通用性范围极大,技术覆盖面涉及所有板级电路的电子产品,技术应用具备极广,尤其在高密度板级电路的可制造性设计、可测试性设计研究及实施应用等方面创立一个新途径,力争?谙低承訮CB设计的项目和流程管理上有所建树。

项目技术指标在国内处于领先地位,相当于国际上90年代末SMT技术水平,基本上是中视频频段和小功率范围,没有涉及微波、毫米波频段及大功率范围。微波、毫米波频段及大功率范围的板级电路高密度、 我们2002年在《板级电路高密度、高精度组装技术》试验中所采取的“叠层”组装设计和工艺技术,就是近几年在全球掀起的元器件堆叠装配(POP,Package on Package)技术。 元器件堆叠装配(POP,Package on Package)技术的出现,进一步模糊了一级封装与二级组装之间的界线,在大大提高逻辑运算功能和存储空间的同时,也为用户提供了元器件组合装配的可能,生产成本得以更有效的控制,由此,元器件堆叠装配是一种值得考虑的优选方案;毫无疑问,随着元器件小型化高密度封装的发展,对于高速与高精度装配的要求将变得更加关键,相关的组装设备和工艺技术也更具先进性与高灵活性,元器件堆叠装配(POP,Package on Package)技术必将经受这一新的挑战。 | |